앞서 말했듯,전원 품질(Good PDN)을 확보하려면 IR Drop 최소화, Decoupling Capacitor의 배치, Stackup이 핵심이다. 이에 대해 자세히 살펴보자.

1. IR Drop 최소화

회로 전체의 DC 저항이 커지면 해당 부분에서 불필요한 에너지의 소모(발열)이 발생하고, 이로 인해 IR Drop이 발생하게 된다. 이를 줄이기 위해서 흔히 사용되는 설계 기법은 다음과 같다.

- 전원선 폭과 두께를 최대화

넓고 두꺼운 전원 트레이스는 현대 다층 PCB 설계에서는 선호도가 떨어진다. 전용 파워 플레인을 깔 수 없는 1~2층 보드에서, 전원 안정성이 크게 중요하지 않을 때 사용된다.

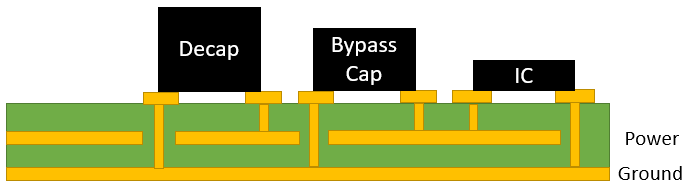

- 넓고 두꺼운 파워/그라운드 플레인 사용

다층 PCB에서 독립 파워/그라운드 레이어 확보하여 전용 파워·그라운드 플레인을 활용하면 전체 면적이 거대한 병렬 저항으로 동작해 IR Drop과 노이즈를 효과적으로 억제할 수 있다.

2. Decoupling Capacitor

디커플링 커패시터를 적절히 배치를 통해서도 PDN의 안정성을 크게 개선할 수 있다. 아래에서는 용량, 크기, ESR/ESL 같은 세부 특성은 잠시 뒤로 하고, 디커플링 커패시터가 가져오는 핵심 효과만을 살펴보자.

1. 순간적인 전류 공급 (대용량(10 µF 이상) Capacitor) -> 배터리 역할

스위칭 소자들이 순간적으로 큰 전류를 요구할 때, PDN은 본래의 전원 공급망만으로는 즉각 대응하기 어렵다. Decoupling Capacitor는 내부에 저장된 전하를 배터리처럼 빠르게 부하가 요구하는 전류를 공급한다.

2. Noise Decoupling (소용량(0.1 µF 이하) 세라믹 캐패시터)

Capacitor는 DC에는 거의 무한대 임피던스지만, 주파수가 높아질수록 임피던스가 낮아지는 특성을 가진다. 고주파 노이즈 성분을 커패시터가 그라운드 쪽으로 흘려보내면서 PDN을 안정화 시켜준다.

| 주파수 | 용량 | 종류 | 배치 | 용도 |

| DC ~ 100 kHz | 10 µF ~ 100 µF | 전해 / 폴리머 / 탄탈 | VRM 인근, PCB 전원 입력단 | 저주파 리플 제거, 높은 ESR로 댐핑 효과 제공 |

| 100 kHz ~ 10 MHz | 1 µF ~ 10 µF | 세라믹 (X5R, X7R) | PCB 레벨 (전원 레일 클러스터) | 중주파수 대역 안정화, 적당한 ESR·ESL |

| 10 MHz ~ 100 MHz | 0.1 µF ~ 1 µF | 세라믹 (X7R, C0G) | IC 전원핀 인근 | 고주파 스위칭 노이즈 억제, 낮은 ESL |

| 100 MHz ~ 500 MHz | 0.01 µF ~ 0.1 µF | 세라믹 (C0G, NP0) | 패키지( BGA) 상부 | 초저 ESL로 패키지-다이 간 고주파 안정화 |

| 500 MHz 이상 ~ GHz 이상 | 수 pF 이하 | 온칩 통합 커패시턴스 | 다이 내부 | 가장 빠른 전류 응답, 패키지/PCB 레이어로는 대응 어려움 |

3. Examples

OP Amp 전원라인의 바이패스 캐패시터(Bypass Capacitor)의 효과

Push-pull 전류증폭회로는 함수발생기보다 훨씬 많은 전류를 출력할 수 있어서, 이 회로를 만능기판에 납...

blog.naver.com

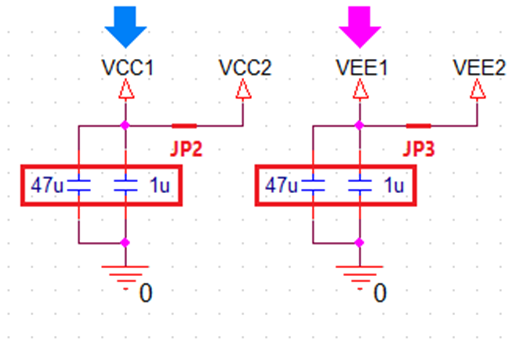

대용량 Decap과 소용량 세라믹 Decap을 병렬 결합해 각각 저주파/고주파 대역을 커버하여 PDN과 SI를 동시에 확보한 좋은 예시가 있어 가져와 봤다.

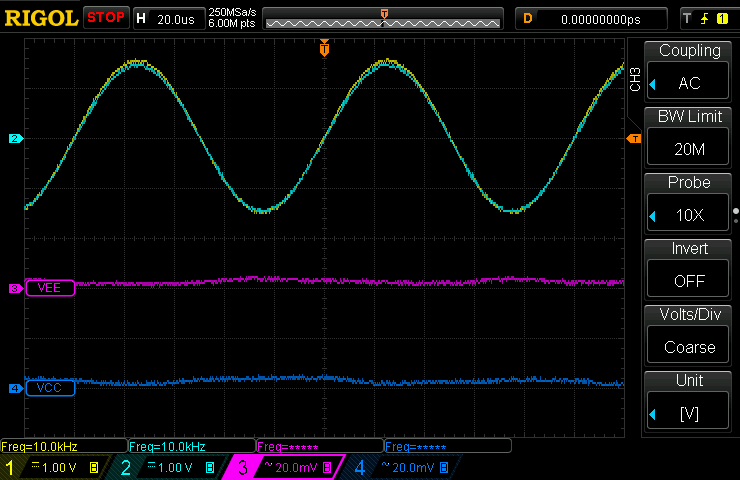

VCC, VEE 전원 라인에 Decoupling Capacitor를 미설치 상태로 초기 테스트 수행했을 때,

- OP Amp 출력부에서 2 MHz 대역의 발진 현상

- 전원 라인(VCC, VEE)에도 동일 주파수 대역의 리플이 크게 발생

하는 것을 보여주고 있다.

이제 아래 Decoupling Capacitor를 전원 Line에 배치하였을 때,

- 1 µF 세라믹 캐패시터: 고주파 노이즈 션트용

- 47 µF 전해 캐패시터: 저주파 리플 완화용

전원 라인 리플이 수백 mV에서 20 mV 수준으로 대폭 감소하고, OP Amp 출력 부의 발진 현상 제거되는 것을 볼 수 있다.

3. PCB Stackup

PCB 스택업은 레이어 수나 순서, 두께, 소재 선택 등 디자이너 역량과 프로젝트 요구사항에 따라 달라지기 때문에 어떤 것이 가장 좋다라고는 할 수 없다. 일반적인 가이드라인은 다음과 같다.

- 전원(POWER) 레이어와 접지(GND) 레이어를 인접

- 대칭 구조를 통해 Power Plane이 커패시터와 같은 역할을 하게함

- POWER/GND 간 유전체 두께를 가급적 얇게 설계

- IC와 가장 가까운 Layer를 Power Layer로 선정

'PCB 이론 > PI' 카테고리의 다른 글

| Target Impedance (0) | 2025.07.23 |

|---|---|

| Voltage? Current? PI에서 진짜 중요한 건 ‘Current’ (0) | 2025.06.27 |

| What is Power Integrity? (0) | 2025.06.27 |