1. Title

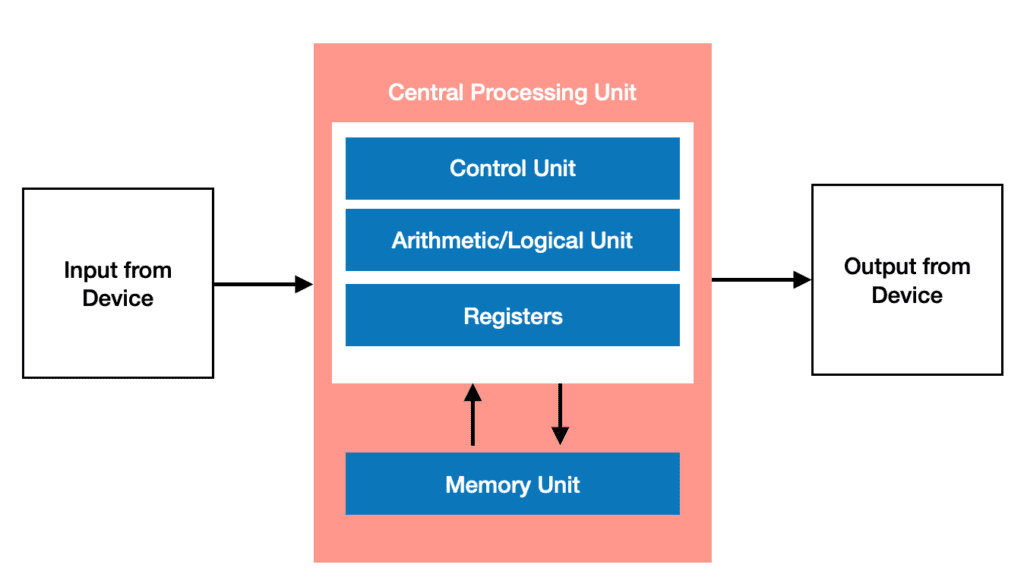

CPU Overview

2. Category

"CPU"

3. Key Concepts

CPU Architecture, RISC, CISC

4. Setup

https://teachcomputerscience.com/von-neumann-harvard-architecture/

폰 노이만 구조

명령어와 데이터를 동일한 메모리에 저장하며, 단일 버스를 사용하므로 병목현상이 발생할 수 있다.

구조는 단순하고 비용이 저렴하여 범용 컴퓨터에서 많이 사용된다.

한 번에 하나의 작업만 수행하므로 메모리 접근 속도가 제한된다.https://teachcomputerscience.com/von-neumann-harvard-architecture/

하버드 구조

명령어와 데이터를 별도 메모리에 저장하며, 각각의 버스를 사용해 성능이 향상된다.고속 처리가 필요할 때 사용되며, DSP(디지털 신호 처리) 분야에서 많이 활용된다.

명령어와 데이터를 동시에 처리할 수 있어 실행 속도가 빠르다.

https://en.wikipedia.org/wiki/RISC-V

본 과정에서는 RISC-V 구조, 그 중에서도 RV32I(32비트 정수 명령어 셋) 기반의 CPU를 설계하게 된다.https://blog.naver.com/gotjdehfdl5/223688070162

** 현대 CPU는 L1 캐시를 명령어 캐시(I-cache)와 데이터 캐시(D-cache)로 분리하여 사용하는 등, 폰노이만 구조와 하버드 구조가 혼합된 형태의 구조를 가진다.

'AI SOC COURSE > SYSTEM VERILOG (CPU 설계)' 카테고리의 다른 글

| CPU Course Review - 06. TestBench Revision (0) | 2025.02.11 |

|---|---|

| CPU Course Review - 05. Accumulator (0 ~ 9) (0) | 2025.02.10 |

| CPU Course Review - 04. Counter (0 ~ 9) (0) | 2025.02.10 |

| CPU Course Review - 02. TestBench (0) | 2025.02.10 |

| CPU Course Review - 01. FIFO (0) | 2025.02.09 |