1. Title

NAND gate

2. Category

"CMOS", "VLSI", "LAYOUT"

3. Key Concepts

Basic Logic Gates in Layout

4. Contents

NAND / NOR

NMOS의 Width가 고정(1μ) 되어 있을 때, Input PMOS의 Width를 조정하는 방법을 보면 NAND Gate가 Area적인 면에서 선호되는 이유를 알 수 있다.2-input NAND Gate

- NMOS: W/L=1μW/L = 1μ (고정)

- PMOS: W/L=4μW/L = 4μ

2-input NOR Gate

이 차이는 Input이 늘어날 수록 더욱 벌어지게 된다.

- NMOS: W/L=1μW/L = 1μ (고정)

- PMOS: W/L=8μW/L = 8μ

SWITCH

여러 입력 신호 중 하나를 선택하여 출력으로 전달하는 회로이며, 주로 MUX 설계에 사용되게 된다.

XOR

두 입력이 반전될 때 '1', 같을 때 '0'을 출력하는 회로이며, ADDER 설계에 사용된다.

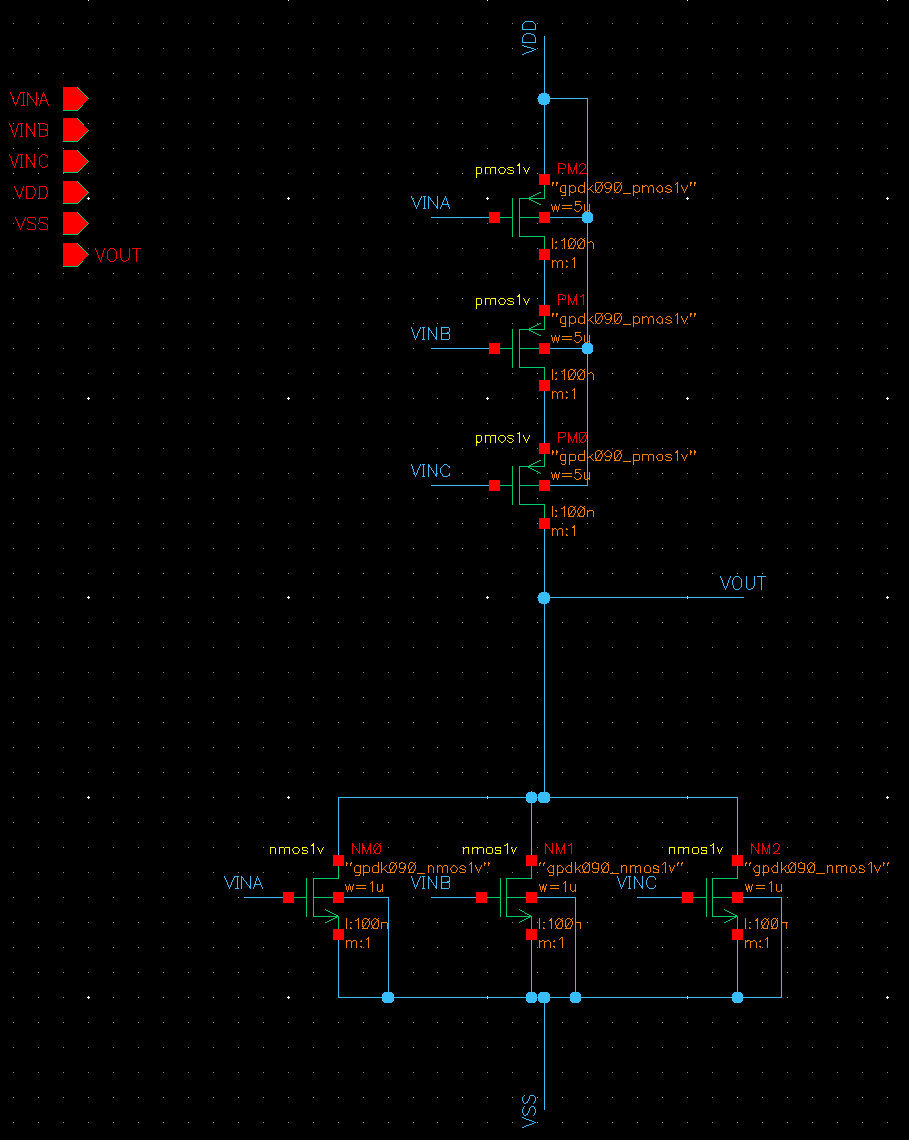

5. Schematic

2,3,4 Input NAND

2,3,4 Input NOR

SWITCH XOR

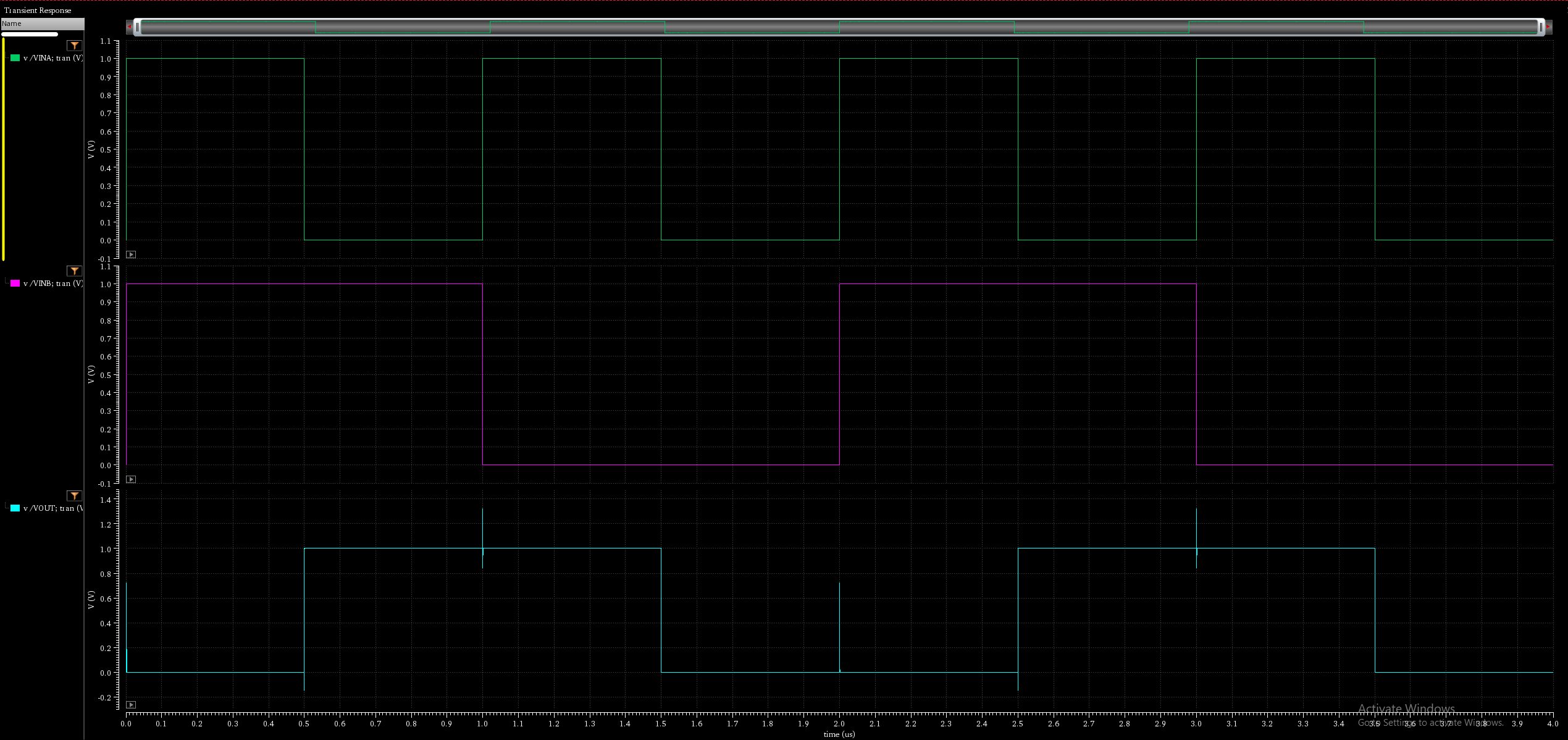

6. Simulation

다중 Input Gate의 경우, 저항값이 선형적으로 달라지지 않기 때문에 Inverter에서 Simulation 했듯이, PMOS WIDTH를 swing 해가며 적절한 WIDTH 값을 찾는다.

NOR의 경우 Input이 0/0/0/0 로 변화할 때에만 Output이 다르기에 위와 같이 설정한다. NAND의 경우 Input이 1/1/1/1 로 변화할 때에만 Output이 다르기에 위와 같이 설정한다.

XOR의 경우 Input을 변경시켜가며 Output을 관찰하기 위해 DC Sweep이 아닌 Transient Analysis를 진행

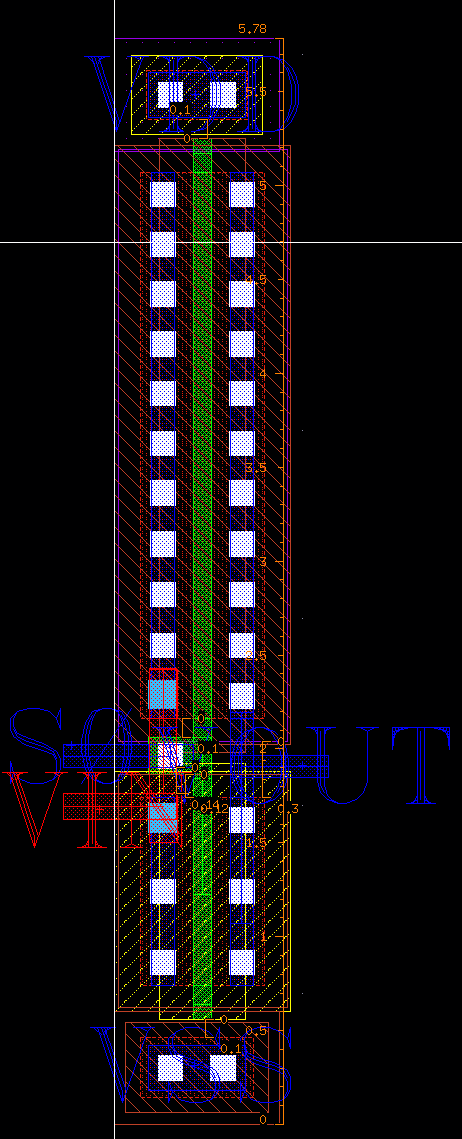

7. Layout & Layout Verification (Assura DRC, LVS)

Logic Gates Logic Gates DRC CHECK

Logic Gates LVS CHECK

NAND GATES

NAND DRC CHECK

NAND LVS CHECK

NOR GATES NOR DRC CHECK

NOR LVS CHECK

SWITCH / XOR GATE

SWITCH / XOR DRC CHECK

SWITCH / XOR LVS CHECK

'AI SOC COURSE > CMOS VLSI' 카테고리의 다른 글

| CMOS VLSI Course Review - 06. Adder, Subtractor (0) | 2025.01.17 |

|---|---|

| CMOS VLSI Course Review - 05. Logic Gate MUX (0) | 2025.01.16 |

| CMOS VLSI Course Review - 04. Switch MUX (0) | 2025.01.16 |

| CMOS VLSI Course Review - 02. INVERTER (0) | 2025.01.13 |

| CMOS VLSI Course Review - 01. Basics (0) | 2025.01.12 |