AMBA AXI(Advanced eXtensible Interface)는 고성능, 확장 가능한 버스 프로토콜로, SoC에서 복잡한 데이터 전송을 처리하기 위해 설계되었다. AXI는 마스터와 슬레이브 간 상호작용을 기반으로 작동하게 된다.

IHI0022K_amba_axi_protocol_spec.pdf

1.52MB

102202_0100_01_Introduction_to_AMBA_AXI.pdf

0.93MB

- 마스터 (Master): 데이터 전송을 시작하고 제어하는 엔티티. 예를 들어, CPU, GPU, DMA 컨트롤러 등이 마스터가 될 수 있다. 마스터는 데이터를 생성하거나 요청(읽기/쓰기)을 보낸다.

- 슬레이브 (Slave): 마스터의 요청에 응답하거나 데이터를 제공/수용하는 엔티티. 예를 들어, 메모리 컨트롤러, RAM, ROM, 주변 장치 등이 슬레이브가 될 수 있다.

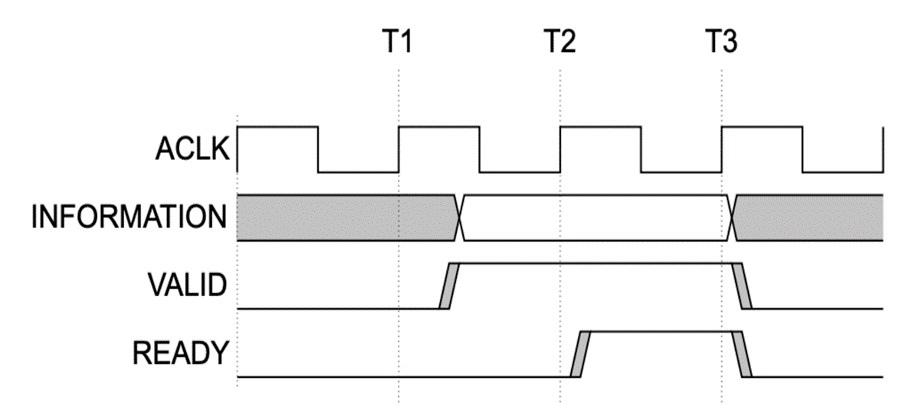

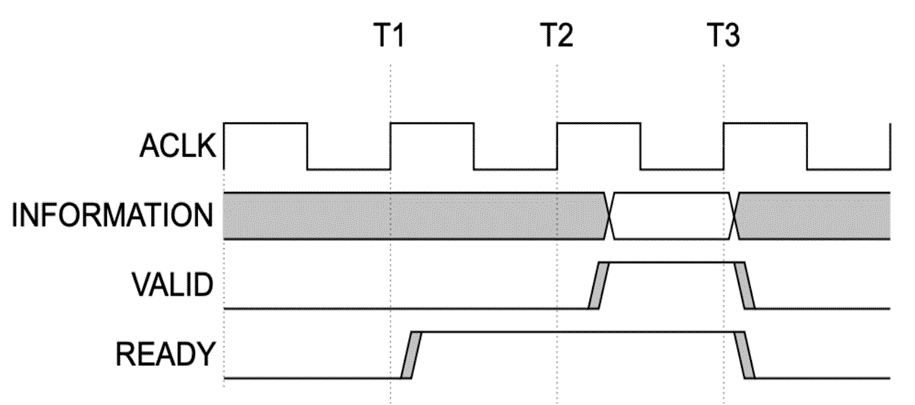

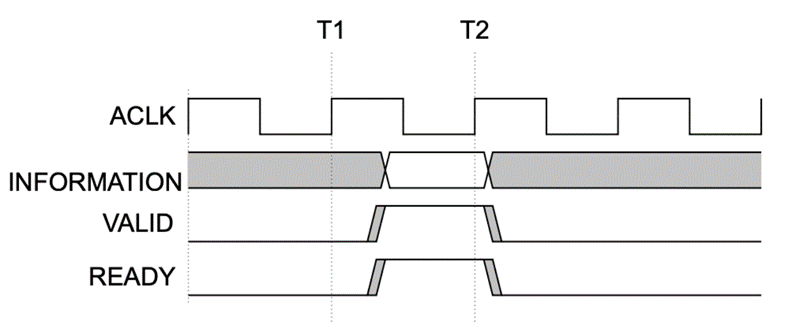

AXI(특히 AXI3, AXI4, AXI4-Lite, AXI4-Stream)에서 사용되는 데이터 전송 메커니즘은 READY/VALID Handshake로써 다음과 같은 특징을 가진다.

읽기 주소 채널, 읽기 데이터 채널, 쓰기 주소 채널, 쓰기 데이터 채널, 응답 채널 등 독립적인 데이터 채널을 가지며, 각 채널은 별도의 VALID와 READY 신호를 사용하여 데이터 전송을 제어하게 된다.

- 읽기 주소 채널 (Read Address Channel): 마스터가 읽기 요청을 슬레이브에 보냄.

- 읽기 데이터 채널 (Read Data Channel): 슬레이브가 마스터에 읽기 데이터를 반환.

- 쓰기 주소 채널 (Write Address Channel): 마스터가 쓰기 요청을 슬레이브에 보냄.

- 쓰기 데이터 채널 (Write Data Channel): 마스터가 슬레이브에 쓰기 데이터를 보냄.

- 응답 채널 (Write Response Channel): 슬레이브가 쓰기 완료 상태를 마스터에 보고.

- VALID: 송신자가 데이터를 사용할 수 있고 전송할 준비가 되었음을 나타내기 위해 이 신호를 설정한다.

- READY: 수신자가 데이터를 수용할 준비가 되었음을 확인하기 위해 이 신호를 설정한다.

VALID와 READY가 모두 높은 상태(논리 1)일 때만 데이터가 흐르는 것을 확인할 수 있다. 이 핸드셰이크는 준비되지 않은 수신자에게 데이터를 보내거나 송신자가 무한정 대기하는 위험을 제거하여 깔끔하고 효율적인 전송 과정을 제공한다.

'AMBA BUS > AXI BUS' 카테고리의 다른 글

| AMBA AXI BUS - 04. VIVADO AXI4-Lite Template 분석 (0) | 2025.03.07 |

|---|---|

| AMBA AXI BUS - 03. AXI4_Lite 설계 (0) | 2025.03.07 |

| AMBA AXI BUS - 02. Example of Ready / Valid Handshake (0) | 2025.02.22 |